- CPUSIM INSTRUCTION MEMORY SOFTWARE

- CPUSIM INSTRUCTION MEMORY CODE

- CPUSIM INSTRUCTION MEMORY PC

- CPUSIM INSTRUCTION MEMORY SIMULATOR

- CPUSIM INSTRUCTION MEMORY WINDOWS

Thus it was possible to advance beyond 320x200 x 256 color VGA limitation to 640x480 SVGA. Also by programming the Hardware through in / out instructions, it was possible to select a different 64-k page at the graphics board. VGA graphics in 8086 architecture was implemented with memory mapping a 64k segment to ISA-bus. The physical address is in 8086 mode calculated as stack_reg * 16 + offset, where trying to read a word at seg_reg: causes an segment violation exception.

CPUSIM INSTRUCTION MEMORY CODE

mov reg, and push/pop are associated with stack segment ss, movs are associated with ds:, es: Program counter / jumps are associated with code segment cs. Then 8086 had segmented architecture, where every memory access is coupled with implicit or explicit segment register. In order to access the next 256 bytes, the instruction itself was modified to read lda $1300,Y for example. At any time, that kind of instruction saw a window of 256 bytes. The 6502 had indexed memory read instructions lda $01200,Y and lda $1413,X where the 16-bit address was encoded as part of the instruction. L1: ADD r7, r8 BR L1 When the branch instruction above is encountered, the program counter is set to the address of the instruction ADD r7, r8, so that it will be the next.

CPUSIM INSTRUCTION MEMORY WINDOWS

CPUSIM INSTRUCTION MEMORY PC

PIC microcontrolers have 8-bit value in registers merge with the high bits in PC (or some dedicated address register, as I don't remember) to form 13-bit address (or more, depend on architecture)Īnother common way in microcontrollers (some microprocessor architectures) is banking, in which you change the "memory window" that the CPU can see each time. The 32-bit x86 uses 36 bit address with PAE. 80286 uses 24-bit address with the high 16-bit segment is an index into a table of segment descriptors. The 16-bit 8086 has 20 bit address with segmentation. The Intel 8080 is an 8-bit CPU with 2 registers H and L for indirect address, allowing it to address 16-bit of memory. There are lots of techniques to achieve this

Those 16-bit instructions are slow, they actually do a pair of 8-bit operations in succession. it can read or write just a single byte of memory at a time, so they are 8-bit on hardware level too. And their memory accessing unit is 8-bit, i.e.

CPUSIM INSTRUCTION MEMORY SOFTWARE

they can compute math and other arithmetic stuff only in an 8-bit register, so they are 8-bit on a software computation level. Those old 8-bit CPU's use an 8-bit accumulator, i.e. You can do indexed addressing on it like this: mov ix, 8002h base address of an array For example Zilog Z80 is called 8-bit CPU but it also contains many 16-bit instructions. It always depends on a particular CPU architecture.

with just a single register and an immediate address: mov h, 80h

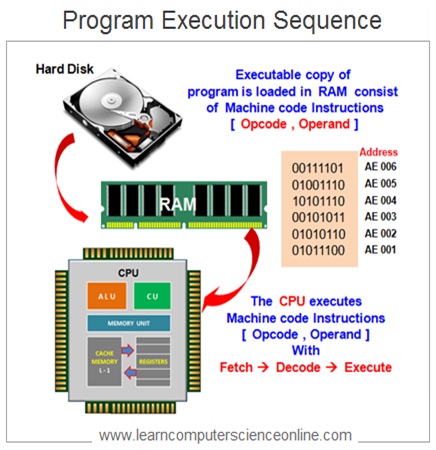

For example, we want to read byte from address 32770 dec = 8002 hex. This app is primarily intended to help teach ‘4.7.3.2 The Fetch-Execute cycle and the role of registers within it’ of the AQA A-Level specification, using the Harvard Architecture.Let's imagine we have LOWER and HIGHER 8bit half of the address in registers L and H. This is a document-based application which means that you can create and run an unlimited number of unique simulations, save and share them. Specifically, the fetch-decode-execute cycle and how components of the processor change at each stage – depending on the code being run.Īn interactive interface shows the components of the CPU, their contents, a description of what has changed in one clock cycle, an IDE to develop assembly code, an interface to view corresponding machine code, an interface to change preferences and more.

CPUSIM INSTRUCTION MEMORY SIMULATOR

CPU Simulator is intended for students studying A-Level AQA Computer Science, who need to understand certain information on how a computer’s CPU functions.

0 kommentar(er)

0 kommentar(er)